硬件工程师必知必会的 Xilinx FPGA 知识

现场可编程门阵列(FPGA,Field Programmable Gate

Array)是一种高性能、低延时、可重构,拥有高速并行运算能力,并可定制性能与功耗的可编程数字逻辑芯片,最早由

1984

年创立的赛灵思(Xilinx)公司推出,该公司由

Ross H. Freeman 和 Bernard V. Vonderschmitt

共同创办。不同于专用集成电路(ASIC,Application

Specific Integrated Circuit)固定的内部电路连接和逻辑功能。FPGA

的内部电路连接和逻辑功能,都可以通过编程来灵活的定义。

目前全球 FPGA 的市场份额主要集中在赛灵思(Xilinx,2020 年被 AMD 收购)和阿尔特拉(Altera,2015 年被 Intel 收购)两家美国企业手中,余下的市场份额同样由美国的莱迪思(Lattice)和美高森美(Microsemi)两家公司占据。国产 FPGA 芯片产业起步较晚,产品性能与专利积累较为薄弱,目前主要有 深圳紫光同创、上海安路科技、广东高云半导体、上海复旦微电子、西安智多晶、深圳易灵思、北京京微齐力、成都华微电子 等芯片研发厂商。

AMD/Xilinx 产品线介绍

AMD/Xilinx 公司的 现场可编程门阵列(FPGA,Field Programmable Gate Array)产品线,主要可以划分为 7 系列、UltraScale 系列、UltraScale+ 系列 三个大系列:

- 7 系列:采用

28nm制程工艺,包含Spartan-7、Artix-7、Kintex-7、Virtex-7四个子系列; - UltraScale 系列:采用

20nm制程工艺,包含Kintex UltraScale、Virtex UltraScale两个子系列; - UltraScale+ 系列:采用

16nm制程工艺,包含Spartan UltraScale+、Artix UltraScale+、Kintex UltraScale+、Virtex UltraScale+子系列;

在上述三个大系列的基础之上,面向不同的应用场景,上述每一个系列会被进一步划分为 Spartan、Artix、Kintex、Virtex 四个子系列:

- Spartan 系列:低成本低功耗,面向消费电子和基础应用;

- Artix 系列:平衡成本与性能,适用于低功耗中等算力场景;

- Kintex 系列:高性能计算与通信,同时兼顾性价比;

- Virtex 系列:旗舰级高性能,用于最苛刻的应用;

AMD/Xilinx 公司也推出了同时集成有 Soc 和 FPGA 的四种自适应 Soc(Adaptive SoCs)产品线:

- 7000 SoC:采用 28nm

制程工艺,集成有单/双核

ARM Cortex-A9,拥有12.5G速率的收发器; - UltraScale+™ MPSoC:采用 16nm

制程工艺,集成有双/四核

ARM Cortex-A53、双核ARM Cortex-R5F、ARM Mali-400MP2和 H.264/H.265 视频编解码器。 - UltraScale+ RFSoC:采用 16nm 制程工艺,集成有四核

ARM Cortex-A53、双核ARM Cortex-R5F和数字RF-ADC、RF-DAC、SD-FEC,广泛应用于 5G 通信、雷达、卫星通信等领域。 - AMD Versal Adaptive SoC:采用 7nm

制程工艺,集成有双核

ARM Cortex-A72、双核ARM Cortex-R5F,以及 DSP 和 AI 引擎与可编程片上网络,主要应运用于人工智能场景。

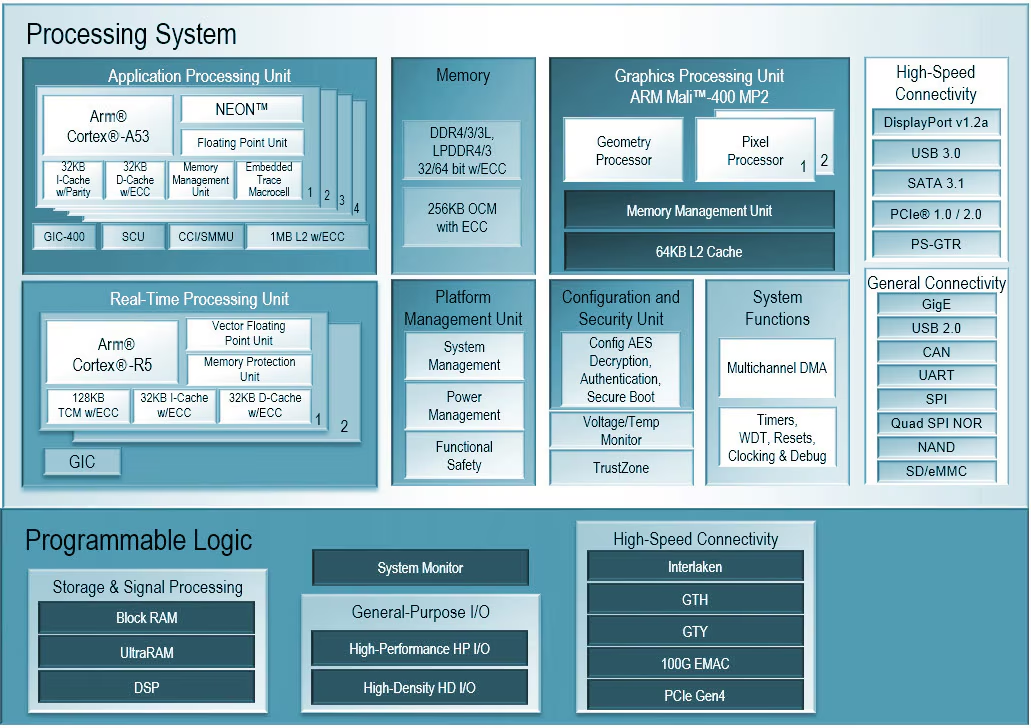

AMD/Xilinx 公司目前力推的 UltraScale+ 系列 多处理器片上系统(MPSoC,Multi-Processor System on Chip)产品,属于集成有多种异构处理核心的高性能片上系统,主要内置有如下的片上计算资源:

- 应用处理器 APU:多核 64 位

ARM Cortex-A53,可运行 Linux 操作系统,负责通用计算; - 实时处理器 RPU:双核

ARM Cortex-R5F,用于处理实时任务; - 图形处理器 GPU:

ARM Mali-400MP2用于处理显示输出任务; - 可编程逻辑

PL:

UltraScale+ FPGA,用于实现硬件加速; - 视频编解码:用于支持

H.264/H.265视频编解码;

而 UltraScale+ MPSoC 主要涵盖了 CG、EG、EV、RF 如下四个子系列:

- CG 子系列:入门级器件,主要集成有

双核 1.3 GHz ARM Cortex-A53和双核 ARM Cortex-R5F,系统逻辑单元数量在81K ~ 600K范围; - EG 子系列:资源较为丰富,主要集成有

四核 1.5 GHz ARM Cortex-A53、双核 600 MHz ARM Cortex-R5F、ARM Mali-400MP2,系统逻辑单元数量在81K ~ 1143K范围; - EV 子系列:内置视频编解码器,主要集成有

四核 1.5 GHz ARM Cortex-A53、双核 600 MHz ARM Cortex-R5F、ARM Mali-400MP2、H.264/H.265 视频编解码器,系统逻辑单元数量在192K ~ 504K范围;

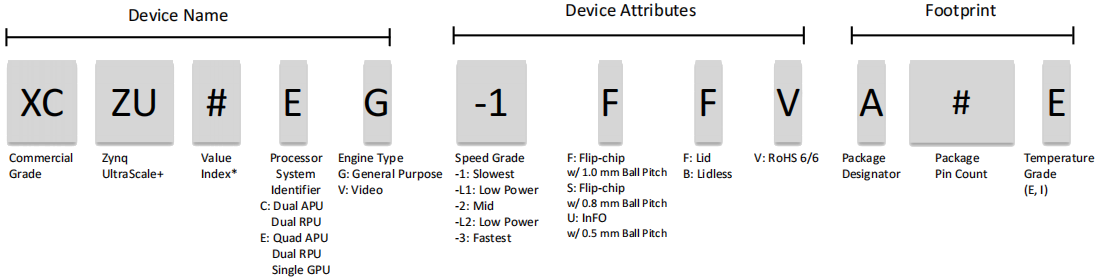

MPSoC 命名规则

UltraScale+ MPSoC 系列产品的命名由

设备名称 + 设备属性 + 封装信息 构成,例如对于命名为

XCZU7EV-2FFV C1156I 的 MPSoC 芯片:

设备名称 部分是 XCZU7EV:

- 商品级别:XC 表示 Xilinx Commercial 公司;

- 产品系列:ZU 表示

Zynq UltraScale+系列; - 价值索引:该数值越大,片上资源就越丰富,价格也就越高;

- 处理器系统标识符:C 代表双核 APU 和双核 RPU,E 代表四核 APU、双核 RPU、单个 GPU;

- 引擎类型: G 表示通用,V 表示带有视频解码器;

制造工艺 部分是 -2FFV:

- 速度等级:

-1/2/3表示最慢/中等/最快,-L1/L2表示低功耗; - 倒装封装:F 表示球距

1.0 mm的 Flip-chip 封装,S 表示球距0.8 mm的 Flip-chip 封装,U 表示球距0.5 mm的 InFO 封装; - 封装技术:F 表示

Lid封装技术,B 表示Lidless封装技术; - 电气标准:V 表示符合 RoHS 六项检测;

封装信息 部分是 C1156I:

- 封装标识符:例如

A或者C等; - 封装引脚数量:例如

1156等; - 温度等级:E 表示工作在

0°C ~ +100°C,I 表示工作在–40°C ~ +100°C;

处理系统 PS / 可编程逻辑 PL

AMD/Xilinx 的 MPSoC 系列 FPGA 芯片主要由 处理系统(PS,Processing System)和 可编程逻辑(PL,Programmable Logic)两个核心部分组成(两者可以分别独立供电与断电),下图展示了 XCZU7EV 的系统架构图:

- 处理系统(PS,Processing System):基于 ARM Cortex 架构,类似于传统的 CPU 中央处理器,可以直接运行嵌入式 Linux 操作系统;

- 可编程逻辑(PL,Programmable Logic):传统的 FPGA 可编程逻辑资源,支持硬件并行处理,可通过 Verilog 或者 VHDL 进行编程;

注意:PS 和 PL 之间通过 FPGA 片内的高级可扩展接口(AXI,Advanced eXtensible Interface)总线进行高速数据传输。

可编程逻辑 PL

简化的 FPGA 基本结构分别由

可编程输入/输出单元、基本可编程逻辑单元、嵌入式块 RAM、布线资源、底层嵌入功能单元、内嵌专用硬核

六个部分组成:

FPGA 的输入/输出单元被设计为可编程模式,可以通过开发工具灵活的进行配置,从而适配不同的电气标准与 I/O 物理特性(可以调整匹配阻抗特性、上下拉电阻、驱动电流的大小等)。

处理系统 PS

串行解串器 SerDes

FPGA 内置的串行解串器(SerDes,Serializer/Deserializer)用于进行串行数据与并行数据的相互转换:

- 当 FPGA 作为接收端的时候,用于将串行数据,转换为 FPGA 内部能够处理的并行数据。

- 当 FPGA 作为发送端的时候,用于将 FPGA 内部的并行数据,转换为便于传输的串行数据。

注意:现代 FPGA 通常集成了专用的 SerDes 外设,例如 AMD/Xilinx 的

GTX/GTH/GTY收发器,以及 Intel/Altera 的Transceiver收发器。

查找表 LUT

查找表(LUT,Look-Up Table)是现场可编程门阵列 FPGA 当中的基本逻辑单元,用于实现组合逻辑功能。

简单的来说,就是将某个简单逻辑功能的全部可能结果写到一个存储单元中,并根据输入的变化直接查找结果并输出。

MIO/EMIO 多路复用 IO

AMD/Xilinx FPGA 提供了多路复用(MIO,Multiplexed IO)和扩展多路复用(EMIO,Extended Multiplexed IO)两种 I/O 管理机制:

- MIO:由处理系统 PS 直接管理的物理引脚,无需经过 PL 可编程逻辑单元,可以控制 PS 的各种外设;

- EMIO:由处理系统 PS 通过 PL 可编程逻辑扩展的 I/O 接口,当 PS 的 MIO 数量不足时,可通过 PL 路由出更多的 EMIO(会引入额外延迟);

I/O Bank

FPGA 的器件管脚按照 Bank 进行划分,通过为每个 Bank

独立供电(通过接口电压 VCCO

进行配置),适配不同的信号电平标准,从而增强 I/O 设计的灵活性。每组用户

Bank 可以包括 52 个 HP 或者

HR 的 I/O 引脚,或者 24 组

HD 的 I/O 引脚(由 48 个差分引脚和 4

个单端引脚组成):

- 高性能(HP,High

Performance):应用于高速场景,工作电压通常在

1.0V ~ 1.8V范围(电平的电压越低,通信速率就会越快); - 宽范围(HR,High

Range):应用于宽范围电压场景,可以支持

1.2V ~ 3.3V的宽范围工作电压; - 高密度(HD,High Density):每个

Bank 通常由 24 个 I/O 构成,可以支持

1.2V ~ 3.3V;

串行解串器 SerDes

FPGA 内置的串行解串器(SerDes,Serializer/Deserializer)用于进行串行数据与并行数据的相互转换:

- 当 FPGA 作为接收端的时候,用于将串行数据,转换为 FPGA 内部能够处理的并行数据。

- 当 FPGA 作为发送端的时候,用于将 FPGA 内部的并行数据,转换为便于传输的串行数据。

注意:现代 FPGA 通常集成了专用的 SerDes 外设,例如 AMD/Xilinx 的

GTx收发器,以及 Intel/Altera 的Transceiver收发器。

吉比特收发器 GTx

AMD/Xilinx 的 FPGA 产品当中集成的 SerDes

外设被称作吉比特收发器(GT,Gigabyte

Transceiver),基于不同的数据传输速率及其所具备的高级特性,规格书当中会分别以

GTx 格式进行命名,例如

GTP、GTX、GTH、GTZ、GTY。对应于

AMD/Xilinx 的不同产品系列,GTx

的传输速率也会有所不同:

| 7 系列 | UltraScale 系列 | UltraScale+ 系列 |

|---|---|---|

GTP = 6.6 Gb/s |

GTH = 16.3Gb/s |

GTH = 16.3Gb/s |

GTX = 12.5 Gb/s |

GTY = 30.5Gb/s |

GTY = 32.75Gb/s |

GTH = 13.1 Gb/s |

- | - |

GTZ = 28.05 Gb/s |

- | - |

赛灵思 FPGA 最小系统

插入损耗(IL,Insertion

Loss)是指由于元器件插入传输线路之前与之后,信号传输功率损耗的差值,通常使用单位分贝

dB 来进行表示。

下面的图片展示了 XCZU5EG 的系统架构框图:

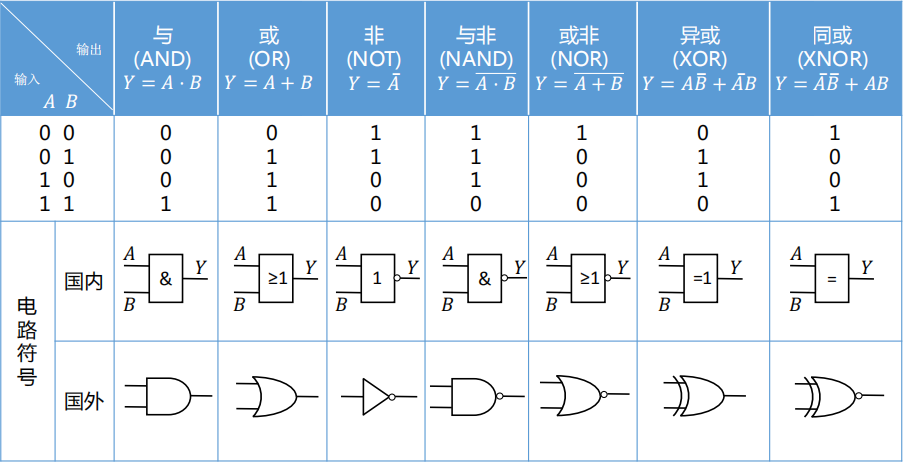

基本的数字逻辑门

门电路是数字集成电路当中,最为基本的逻辑单元,用于实现基本逻辑运算

与、或、非,以及复合逻辑运算

与非、或非、异或、同或,对应的逻辑运算门电路有

与门、或门、非门、与非门、或非门、异或门、同或门,其电路符号如下图所示:

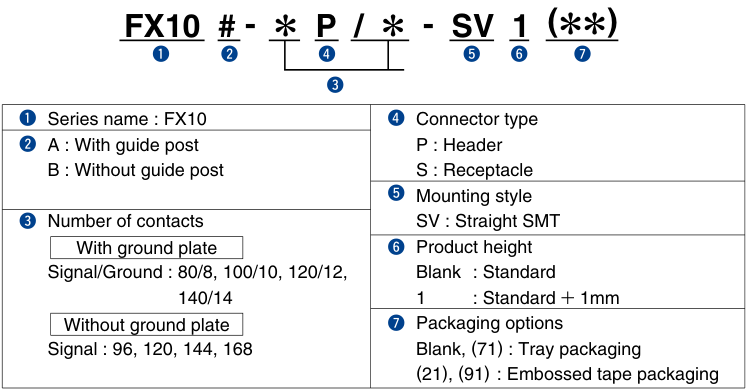

广濑 FX10 高速堆叠连接器

FX10 是日本广濑推出的一款 0.5mm

间距高速堆叠连接器,其最高传输速率可以达到 15+ Gbps:

硬件工程师必知必会的 Xilinx FPGA 知识