基于树莓派 UINIO-MCU-RP2040 核心板制作逻辑分析仪

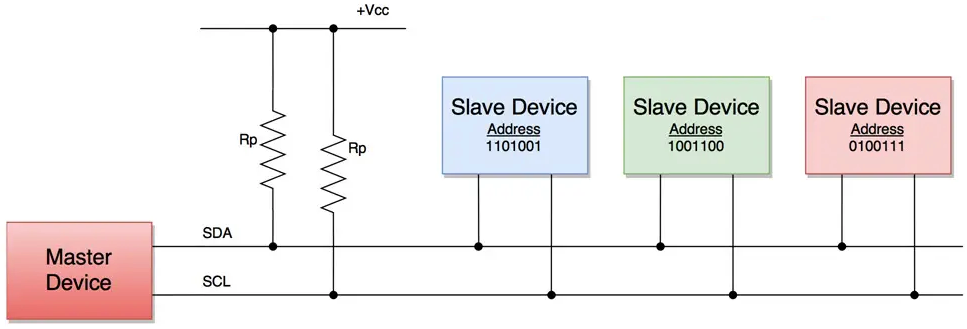

树莓派 RP2040 是一款采用 ARM

Cortex-M0+ 双核心的微控制器,运行频率高达

133MHz,片上内置有 264KB 容量的

SRAM 内存,并且能够外接高达 16MB

容量的片外 Flash 闪存(通过 QSPI

总线连接),内部还集成有 DMA 控制器,以及 30 个 GPIO

引脚(其中 4 个可用作模拟输入)。除此之外,片上还拥有 2 个

UART 控制器、2 个 SPI 控制器、2 个

I²C 控制器、16 个 PWM 通道,以及 2

个可编程 PIO(Programmable I/O)块,并且支持

USB 1.1 主机和设备模式。

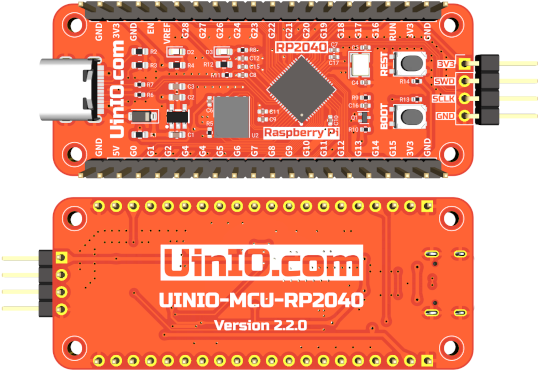

UINIO-MCU-RP2040

是一款基于 RP2040 的开发板,板载 Flash 采用更为小巧的

WSON8 封装,添加 SOD123

封装的肖特基势垒二极管防止正负级反接,同时增加用于全局异步复位的

RESET 按钮,并且引出了官方 Pico 开发板所没有的

GPIO23 和 GPIO24

两个引脚资源。除此之外,由于模数转换引脚内部集成有连接至

IOVDD 的反向二极管,所以采用 FET 场效应管

DMG1012T 防止 RP2040 未上电时,这些引脚上施加的电压通过

ADC3 引脚泄露至 3.3V 电源网络。

硬件设计概要

树莓派基金会于 2021 年初推出的

RP2040 是一款基于台积电 40nm

工艺的低成本、高性能微控制器产品,采用了高达 133MHz

主频的双核心 ARM Cortex-M0+ 内核架构,拥有多达 30

个多功能 GPIO 引脚(其中 4

个可以用作模拟输入),片上载有 264kB

的静态随机存储器 SRAM。除此之外,通过 QSPI

总线还可以支持高达 16MB 的片外 Flash

闪存,下图展示了 RP2040 芯片各个功能引脚的分布:

而接下来的表格,则描述了上图当中 RP2040 各个引脚的具体功能:

| 引脚名称 | 功能描述 |

|---|---|

| GPIOx | 通用数字输入输出引脚,可以将多个内部外设映射至 GPIO。 |

| GPIOx/ADCy | 具有模数转换功能的通用数字输入输出引脚,用于采集电压信号。 |

| QSPIx | 用于连接 SPI、Dual-SPI、Quad-SPI 接口的 Flash 存储芯片,如果未连接,则也可以复用为可编程的 GPIO 引脚。 |

| USB_DM 和 USB_DP | USB 控制器引脚,支持全速的设备(Device)模式,以及全速/低速的主机(Host)模式,必须分别串接 27Ω 的终端电阻。 |

| XIN 和 XOUT | 用于连接 12MHz 频率的晶体振荡器。 |

| RUN | 全局异步复位引脚(低电平复位,高电平运行),如果不需要外部复位,则该引脚可以连接至

IOVDD。 |

| SWCLK 和 SWDIO | SW 串行调试引脚,用于调试和下载固件。 |

| TESTEN | 工厂调试模式引脚,需要接入

GND 使用。 |

| GND | 外部接地引脚。 |

| IOVDD | GPIO 的数字电源引脚,额定电压介于

1.8V ~ 3.3V 范围。 |

| USB_VDD | 内部 USB 全速 PHY 电源引脚,额定电压为

3.3V。 |

| ADC_AVDD | 模数转换器电源引脚,额定工作电压为

3.3V。 |

| VREG_VIN | RP2040

内核稳压器电源输入引脚,额定电压介于

1.8V ~ 3.3V 范围。 |

| VREG_VOUT | RP2040

内核稳压器电源输出引脚,额定电压为

1.1V,最大输出电流为 100mA。 |

| DVDD | 数字核心电源引脚,额定电压为

1.1V,可以连接至上面的 VREG_VOUT。 |

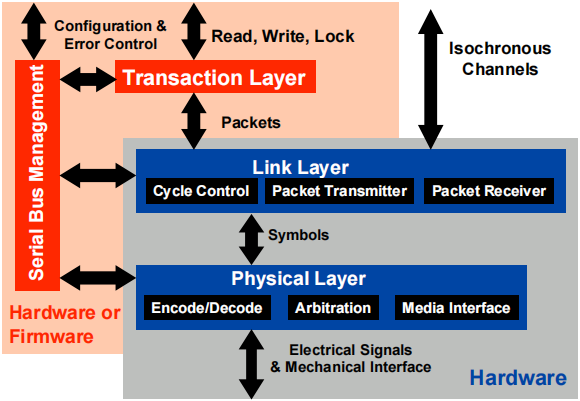

下面展示了 RP2040 微控制器芯片内部的系统结构框图:

- 内嵌的

264kB容量 SRAM 分布在 6 个独立的 Bank 区块,可以通过专用的 AHB 总线进行访问; - 固件程序运行在采用 QSPI 接口的外部 Flash 存储器当中,调试工作则需要通过 SWD 串行线进行。

- 分别拥有

2个 UART、2个 SPI、2个 I²C 总线控制器,以及16条 PWM 通道; - 支持

Host和Device模式的 USB 1.1 控制器以及用于物理信号转换的 PHY(Physical Layer)接口; - 通过 2 个 PLL 锁相环来生成 USB 以及内核的时钟信号;

UINIO-MCU-RP2040 的最小系统主要由电源、Flash 存储器、晶振、输入输出四个部分构成,接下来的内容将会分别进行讨论。

3.3V 线性稳压电路

UINIO-MCU-RP2040 采用 北京圣邦微电子

推出的 SGM2019-3.3YN5G

低压差线性稳压芯片,采用 SOT-23-5 封装,能够提供最大

300mA 的输出电流(此时压差为

400mV),输入电压范围为

2.5V ~ 5.5V,输出电压为 3.3V,下图是官方提供的

SGM2019-3.3YN5G 的典型应用电路:

圣邦微的 SGM2019-3.3YN5G 相比于微盟电子的

ME6211C33M5G 线性稳压芯片,其最大的特点在于提供了一个

EN 输入使能引脚,UINIO-MCU-RP2040

已经将该引脚连接至杜邦排针,并且与核心板的 GND

相毗邻,可以方便的使用跳线帽禁用电源输入,当然也可以用于逻辑控制核心板的运行与停止。下面的表格,提供了

SGM2019-3.3YN5G 全部引脚的功能说明:

| 引脚编号 | 引脚名称 | 功能描述 |

|---|---|---|

1 |

IN | 稳压输入引脚

2.5V ~ 5.5V,需要连接 1uF 的接地电容。 |

2 |

GND | 接地引脚。 |

3 |

EN | 输入使能引脚,低电平时可以将输入电流降低至

10nA,通常将其连接至输入电压引脚 IN。 |

4 |

BP/FB | 参考噪声旁路(仅限固定电压版本)。旁路采用低漏 0.01μF 陶瓷电容,降低输出噪声。 |

5 |

OUT | 3.3V 稳压输出引脚。 |

注意:树莓派 RP2040 需要使用到两种不同的工作电压,其中

3.3V主要用于输入输出,而1.1V则是用于数字核心。由于芯片内部已经集成有3.3V转1.1V的 LDO 低压差线性稳压器,所以硬件电路当中不需要再考虑1.1V电压的供电问题,直接把 VREG_VOUT 与 DVDD 连接起来即可。

电源去耦电容

除此之外,电源设计当中另外一个需要关注的方面在于 RP2040 电源引脚的去耦电容,它们在电路当中可以提供如下两个基本功能:

- 过滤掉一部分电源噪声纹波;

- 防止电流需求突然增大时,电源网络产生过大的压降;

UINIO-MCU-RP2040 采用官方推荐的容值分别为

0.1uF(有效滤除 10MHz 以下的电源纹波)和

2.2uF(有效滤除 20MHz

以上的高频纹波)的贴片陶瓷电容器(0402

封装)作为去耦电容,并且将它们全部放置在靠近 RP2040

芯片电源引脚的位置:

除此之外,由于 RP2040 需要通过

SGM2019-3.3YN5G 线性稳压器,将输入到 VREG_IN

引脚的 3.3V 电压转换为 VREG_OUT 输出的

1.1V 电压(最大输出电流为

100mA),所以这里需要将 VREG_OUT

连接至数字核心的 1.1V 电源输入引脚

DVDD,此时依然分别需要添加相应的去耦电容。

Flash 存储器

RP2040 微控制器运行的固件程序代码都被保存外部的

Flash 存储器当中,UINIO-MCU-RP2040 核心板采用 台湾华邦电子

推出的 W25Q128JVP 型 Flash 存储器,封装形式为更加小巧的

WSON8,选型容量为 128Mbit(即

16MB),也就是 RP2040

微控制器可以支持的最大存储容量:

QSPI_SS 片选引脚连接的 1.5kΩ 电阻为连接到

3.3V 电源的上拉电阻,虽然

QSPI_SS 引脚自动默认为上拉,但是在 RP2040

上电的某个瞬间,无法确保其始终的处于高电平状态,所以这里增加了一枚上拉电阻器来确保该片选引脚始终处于上拉状态。除此之外,在靠近

Flash 存储芯片的电源引脚位置,同样也添加了一枚 0.1uF

的去耦电容。

注意: 由于连接 Flash 存储器的 QSPI 总线频率较高,需要采用尽可能短的 PCB 走线距离,从而确保信号的完整性,并减少周边电路带来的串扰。

BOOT 与 RESET 按键

相较于官方的 Raspberry Pi Pico 开发板只拥有一枚【BOOT】按键,为了方便日常开发使用,UINIO-MCU-RP2040 核心板同时提供了【BOOT】和【REST】两枚按键,其原理图与功能说明分别如下所示:

- 【BOOT】按键:通过一枚

1kΩ电阻连接至 Flash 存储芯片的 SPI 片选引脚,用于失能 Flash 片选信号,从而选择强制从 USB 启动。此时 RP2040 会呈现为 USB 大容量存储设备,可以用于直接复制下载固件。 - 【REST】按键:默认情况下

RUN引脚通过10kΩ上拉电阻钳位在高电平,从而保持核心板处于正常运行状态。而该按键可以将全局异步复位引脚RUN下拉为低电平状态,从而配合【BOOT】按键进入下载引导模式。

注意:按键并联的

0.1uF电容用于滤除被按下时产生的抖动信号,实际应用时可以选择不进行贴装。

晶振电路

虽然 RP2040 拥有内部的时钟源,但是其工作状态容易受到电源电压和温度的影响,因此官方建议使用一个更加稳定和精确的外部时钟源。RP2040 微控制器的外部时钟源可以通过如下两种方式进行提供:

- 将输出

3.3V方波信号的时钟源连接至 RP2040 的XIN引脚; - 在 RP2040 芯片的

XIN和XOUT引脚之间加入12MHz晶体振荡器(首选);

UINIO-MCU-RP2040

选用的是外置石英晶振方案,该款石英晶振的负载电容为

11pF。晶振的负载电容是指与该晶振并联的全部有效电容的总和,可以将其视为晶振电路上串联的一枚电容器,其主要作用是稳定晶振的谐振频率和输出幅度,根据两个电容器并联之后总电容的计算公式:

\[ C_{负载电容} = \frac{C_{对地电容1} \times C_{对地电容2}}{C_{对地电容1} + C_{对地电容2}} + C_{PCB 杂散电容} \]

由于 \(C_{对地电容1}\) 与 \(C_{对地电容2}\) 两枚并联电容的容值相等,而

\(C_{PCB 杂散电容}\) 的容值通常选取在

3pF ~ 5pF 范围,从而可以得到晶振两枚并联的 \(C_{对地电容}\) 的容值计算公式:

\[ C_{对地电容} = (C_{负载电容} - C_{PCB 杂散电容}) \times 2 \]

这里选择 \(C_{PCB 杂散电容}\)

为典型值 5pF,而负载电容 \(C_{负载电容}\) 为

11pF,从而就可以计算得到两枚接地电容的容值分别为:

\[ C_{对地电容} = (11pF - 5pF) \times 2 = 12pF \]

USB 接口电路

RP2040 微控制器提供有 USB_DM 和

USB_DP

两个引脚(无需额外的上拉和下拉),用于全速(FS,Full

Speed)或者低速(LS,Low Speed)的 USB 通信,即可以作为

USB Host(主机),也可以作为 USB Device(设备)。虽然 RP2040 的全速 USB

通信速率被限制为 12Mbps 兆位/秒,但是为了满足 USB

的阻抗规范,依然需要分别串联 27Ω

的终端电阻,并且尽量靠近芯片放置。同时走线需要尽可能的遵循

90Ω 的 USB

差分阻抗规范,并且走线下方尽量保持一个完整的接地平面。

自从 USB Type-C 标准开始,USB 增加了 CC1 和

CC2 两个配置通道(Configuration Channel),当其串联上

5.1kΩ 下拉电阻的时候,表明

UINIO-MCU-RP2040 当前已经被配置为

上行接口(UFP,Upstream Facing Port)用电端,从而提升

USB Type-C 与传统 USB 接口的电源兼容性。

基于树莓派 UINIO-MCU-RP2040 核心板制作逻辑分析仪